# INTERLEAVED BUCK CONVERTER WITH SYNCHRONOUS RECTIFICATION

Vinny Babu (M.Tech Student) Department of EEE MACE Kothamangalam, Kerala, India Ninu Joy (Asst. Professor) Department of EEE MACE Kothamangalam, Kerala, India Smitha Paulose (Asst. Professor) Department of EEE MACE Kothamangalam, Kerala, India

Abstract— A modified Interleaved Buck Converter (IBC) with continuous input current, extremely low output current ripple, low switching losses and improved stepdown conversion ratio is presented in this work. The implemented converter used for synchronous rectification. In this converter, diode is replaced by switch to reduce losses. For this converter, 180 degree phase shifted pulses and its complementary pulses are required. Circuit is simulated with 200V DC input voltage and 24V DC output voltage is verified.

*Keywords*— **Two Phase Interleaved Buck Converter, Continuous Conduction Mode, CIBC, NIBC, MIBC**

#### I. INTRODUCTION

One of the most popular converters for the consumer electronic industry is the DC-DC step-down converter, also known as the buck converter. The synchronous buck converter is straightforward in concept, and is used heavily in consumer electronics. A synchronous buck converter produces a regulated voltage that is lower than its input voltage, and can deliver high currents while minimizing power loss. The new interleaved buck converter has many advantages except power loss in a diodes are high. To reduce power losses, we introduce a synchronous buck converter technique in which diodes are replaced by switches. These switches are operated by complementary pulses of other two switches. By doing this, new interleaved buck converter gets converted into synchronous buck topology. The advantage of using the synchronous buck topology is that it reduces power loss taking place in diode during conduction period which is equal to the product of the forward voltage drop and the current flowing during conduction period.

The rest of the paper is organized as follows. Proposed circuit and modes of operation are explained in section II. Simulation models and results explained in section III. Experimental results are presented in section IV. Concluding remarks are given in section V. II. INTERLEAVED BUCK CONVERTERS

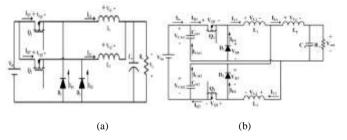

The Fig. 1. (a) shows conventional interleaved buck converter and Fig. 1. (b) is new interleaved buck converter. Conventional IBC problem in high input voltage applications is that the voltage stress of all switches is equal to the input voltage. Due to high voltage stress of switches and diodes, Conventional IBC has high switching losses.

Fig. 1. (a) Conventional (b) New Interleaved Buck Converter

New IBC which suitable for high input voltage, high stepdown, non-isolated applications with low output current and continuous input current. But this converter also having power loss. It is similar to a three level buck converter, but the two input capacitors are not connected to each other and also there is an auxiliary inductor at the converter output stage. The two active switches are controlled by two PWM pulses 180 degrees out of phase.

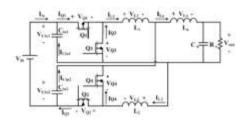

Fig. 2. Modified Interleaved Buck Converter

Synchronous buck converter technique in which instead of diode as shown in Fig. 2. Switches has been used which

complementary operates with its corresponding switch  $Q_3$  which in turn is complementary with  $Q_1$  and similarly  $Q_4$  is complementary with  $Q_2$ . New interleaved buck converter gets converted into synchronous buck topology.

The advantage of using the synchronous buck topology is that it reduces power loss taking place in diode during conduction period which is equal to the product of the forward voltage drop and the current flowing during conduction period.

## A. Modes of Operation -

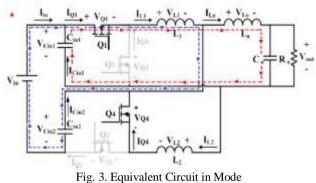

#### Interval 1 [t<sub>0</sub>-t<sub>1</sub>]:

The equivalent circuit of this interval is shown in Fig. 3. Prior to this interval switches  $Q_1$  and  $Q_2$  are off, the  $Q_3$  and  $Q_4$  are ON and the input capacitors  $C_{in1}$  and  $C_{in2}$  are charged. At  $t_0$ ,  $Q_1$  is turned on, so  $Q_3$  turns off. In this interval  $C_{in2}$  is charged through  $V_{in}$  and  $L_1$ , and also  $C_{in1}$  is being discharged through  $L_1$ - $L_0$ - $C_0$ . In addition,  $L_1$  current is increasing through both of the mentioned current paths.  $L_2$  current is decreasing in this state.

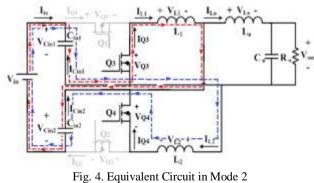

Interval 1 [t<sub>1</sub>-t<sub>2</sub>]:

The equivalent circuit of this interval is shown in Fig. 4. This interval starts when  $Q_1$  turns off. By turning  $Q_1$  off,  $L_1$  continues it's current and turns  $Q_3$  on. Part of the inductor current which was flowing in  $C_{in1}$ - $L_1$ - $L_o$ - $C_o$ , continues its path through  $D_1$ - $L_1$ - $L_o$ - $C_o$ , and the other part of  $L_1$  current runs through  $V_{in}$ - $C_{in1}$ - $Q_3$ - $L_1$ - $C_{in2}$ . So, during this interval,  $L_1$  and  $L_2$  are discharging and  $C_{in1}$  and  $C_{in2}$  are charging through  $V_{in}$ - $C_{in1}$ - $Q_3$ - $L_1$ - $C_{in2}$ - $Q_4$ - $C_{in2}$ .

Fig. 5. Theoretical waveform

Due to symmetric operation of two modules in an interleaved converter, the operations of interval 3 and interval 4 are similar to those of interval 1 and interval 2.

#### III. SIMULATION MODELS AND RESULT

In order to verify the operation principle and the theoretical analysis, conventional, new and modified buck interleaved converters are simulated with MATLAB/SIMULINK simulation software and the simulation parameters are listed in Table 1.

| Table 1 | - Simulation | Parameter |

|---------|--------------|-----------|

|---------|--------------|-----------|

| Parameter              | Specification |

|------------------------|---------------|

| V <sub>in</sub>        | 200V          |

| Vout                   | 24V           |

| Switching<br>Frequency | 100kHz        |

| $L_1 \& L_2$           | 100µH         |

| Lo                     | 5 µH          |

| Cin1 & Cin2            | 4.4µF         |

| Со                     | 1 μF          |

#### A. Simulink Model:

Fig. 6. Simulink Model of CIBC

Fig. 8. Simulink Model of MIBC

Fig. 7 and Fig. 8 shows that simulink model of Newinterleaved buck converter and modified interleaved buck converter respectively. Output voltage, output current ripple, stresses across switches and power losses are analyzed from the simulation results.

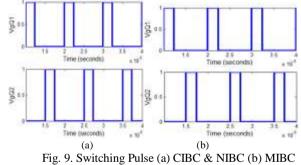

Fig. 9. (a) shows the switching pulse of CIBC & NIBC and Fig. 9. (b) shows the switching pulse of MIBC. The pulse has amplitude of unity with switching frequency of 100kHz. The first pulse has a phase delay of zero and second pulse is a 180 degree phase shifted.

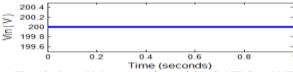

Fig. 10. Input Voltage waveform of CIBC, NIBC and MIBC Fig. 10 shows the input voltage waveform of CIBC, NIBC and MIBC. Input voltage 200V is given to interleaved buck converters.

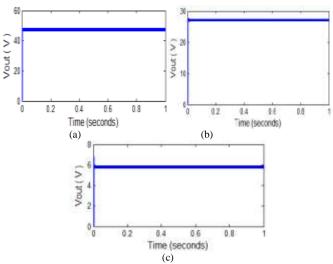

Fig. 11. Output Voltage waveform of (a) CIBC (b) NIBC (c) MIBC

Fig. 11 (a), (b), (c) shows the output voltage waveform of CIBC, NIBC and MIBC respectively. For CIBC, output voltage 47.7V DC is obtained. Output voltage 26.5V is obtained in NIBC and for MIBC, 27.15V is obtained.

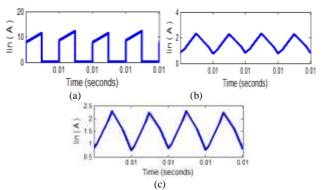

Fig. 12. Input Current waveform of (a) CIBC (b) NIBC (c) MIBC

Fig. 12 (a), (b), (c) shows the input current waveform of CIBC, NIBC, MIBC respectively. For CIBC, input current is discontinuous. Input current for both NIBC and MIBC is continuous.

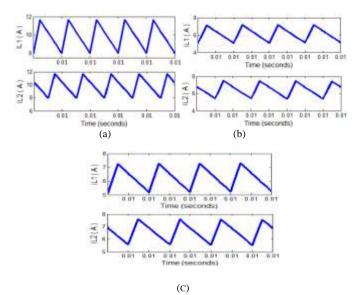

Fig. 13. Inductor Current waveforms of (a) CIBC (b) NIBC (c) MIBC

Fig. 13 (a), (b), (c) shows the inductor current waveforms of CIBC, NIBC and MIBC respectively. Inductor current 11.54A is obtained in CIBC. Inductor current 7.25A is obtained in NIBC. In MIBC, 7.4A is obtained.

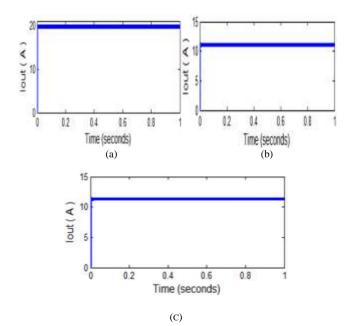

Fig. 14. Output Current waveform (a) CIBC (b) NIBC (c) MIBC

Fig. 14 (a), (b), (c) shows the output current waveform of CIBC, NIBC and MIBC respectively. Output current 19.87A DC is obtained in CIBC. Output current 11.04A is obtained in NIBC and in MIBC, 11.31A is obtained.

Fig. 15. Stress across Switches in (a) CIBC (b) NIBC (c) MIBC

Fig. 15 (a), (b), (c) shows that voltage stress across switches in CIBC, NIBC and MIBC respectively. For conventional IBC, voltage stress across switch 200V is obtained. Voltage stress across switch  $Q_1$  is 125V and  $Q_2$  is 108V is obtained in NIBC. For MIBC, Voltage stress across switch  $Q_1$  and  $Q_3$  is 125V and  $Q_2$  and  $Q_4$  is 108V is obtained.

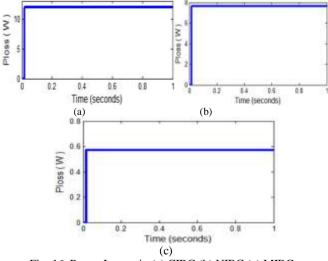

Fig. 16. Power Losses in (a) CIBC (b) NIBC (c) MIBC

Fig. 16 (a) shows power loss of diode in CIBC. Power loss in diode 12W is obtained. Fig. 16 (b) and Fig. 16 (c) shows that power loss in switches for NIBC and MIBC respectively. Power loss in NIBC is 7.621W is obtained. And power loss in MIBC is 0.56W is obtained.

## IV. EXPERIMENT AND RESULT

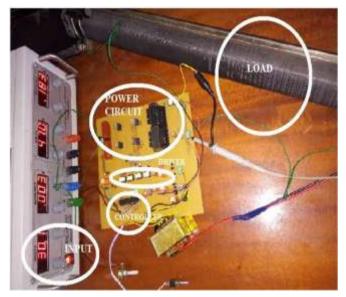

Control circuit and power circuit are implemented in one PCB. Here dsPIC30F2010 is used for generating a pulse and switching frequency. The specification for the hardware is given in Table 2. Hardware is designed for an input voltage of 30V and output voltage of 6V.

| Table -2 Prototype Spe | ecifications |

|------------------------|--------------|

|------------------------|--------------|

| Parameter                       | Specification |

|---------------------------------|---------------|

| V <sub>in</sub>                 | 30V           |

| Vout                            | 6V            |

| Switching Frequency             | 50kHz         |

| L <sub>1</sub> & L <sub>2</sub> | 220µН         |

| Cin1 & Cin2                     | 3.3 µF        |

| Со                              | 100 µF        |

## A. Experimental Setup:

Fig. 17 shows the final hardware prototype of interleaved buck converter for synchronous rectification. The hardware comprises of control circuit and power circuit. Due to the low switch voltage stress of the proposed converter, four power MOSFETs with a rating of 100V and 22A namely, IRF540 is adopted.  $L_o$  is not considered in prototype. In prototype, designed value of output inductor is very small. This small value of inductor does not give any ripple reduction in output current. So, auxiliary inductor is not considered in prototype.

Fig. 17. Experimental Setup

## **B.** Experimental Results:

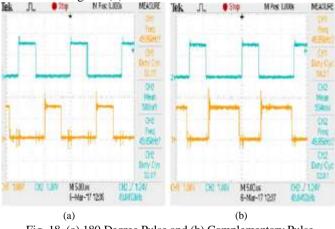

Fig. 18 shows that switching pulse of modified interleaved buck converter. 180 degree phase shifted pulse for switch  $Q_1$  &  $Q_2$  is shown in Fig. 18 (a) and complementary pulse for  $Q_3$  is shown in Fig. 18 (b) obtained from controller.

Fig. 18. (a) 180 Degree Pulse and (b) Complementary Pulse

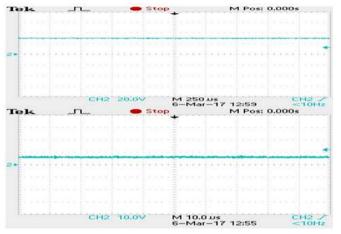

Fig. 19 shows that input and output voltage waveform of proposed converter. Output voltage 6V is obtained from prototype when input voltage 30V is given to modified interleaved buck converter.

Fig. 19. Input and Output Voltage

## V. CONCLUSION

The new interleaved buck converter has many advantages like improved step-down conversion ratio, extremely low output current ripple and low switching losses. Also, the voltage stress of semiconductor components in the new interleaved buck converter and modified interleaved buck converter is much smaller than the conventional interleaved buck converter. Input current is continuous without using any input filter in new interleaved buck converter and modified interleaved buck converter. But in new interleaved buck converter, power loss is much higher. So, we introduce a synchronous buck technology. Two diodes in a new interleaved buck converter are replaced by switches to reduce power loss.

#### VI. REFERENCE

- Y. Jang, M. M. lovanovid and Y. Panov, "Multiphase Buck Converters with Extended Duty Cycle", in Proc. IEEE Applied Power Electronics, pp.38-44, Mar. 2006.

- [2] Y. M. Chen, S. Y. Teseng, C. T. Tsai, and T. F. Wu, "Interleaved buck converters with a single-capacitor turnoff snubber", IEEE Transactions on Aerospace and Electronic Systems, vol. 40, no. 3, pp. 954-967, July 2004

- [3] Il-Oun Lee, Shin-Young Cho, and Gun-Woo Moo, "Interleaved Buck Converter Having Low Switching Losses and Improved Step-Down Conversion Ratio", IEEE Transactions On Industrial Electronics, vol. 27, no. 8, October 2012.

- [4] Morteza Esteki, Nasrin Einabadi, Ehsan Adib, Hosein Farzanehfard, "A High Step-Down DC-DC Converter with Low Switch Voltage Stress and Extremely Low Output Current Ripple", PEDSTC, 16-18 Feb, 2016.

- [5] Morteza Esteki, Behzad Poorali, Ehsan Adib, Hosein Farzanehfard, "High Step-Down Interleaved Buck Converter with Low Switch Voltage Stress", IET Power Electronics, 2015.

- [6] Ching-Tsai Pan, Chen-Feng Chuang and Chia-Chi Chu, "A Novel Transformer less Interleaved High Step-Down Conversion Ratio DC-DC Converter with Low Switch Voltage Stress", IEEE Transactions On Industrial Electronics, vol. 61, no. 10, October 2014.

- [7] Gayathri P Muralidharan, "Interleaved Synchronous Buck Converter with High Conversion Ratio and Voltage Regulation", ICCPCT, 2015.

- [8] Taufik, Randyco Prasetyo, Dale Dolan,"A New Multiphase Multi- Interleaving Buck Converter with Bypass LC", IEEE, 2010.

- [9] Nirmal, Piyush Kumar Jain, and Amit Kumar, "Interleaved DC to DC Buck Converter for Low Power Application", IEEE, 2015.

- [10] Morteza Esteki, Behzad Poorali, Ehsan Adib and Hosein Farzanehfard, "Interleaved Buck Converter with Continuous Input Current, Extremely Low Output Current Ripple, Low Switching Losses and Improved Step-Down Conversion Ratio", IEEE Transactions On Industrial Electronics, 2015.

- [11] Pit-Leong Wong, Peng Xu, Yang. B, Lee. F. C, "Performance improvements of interleaving VRMs with coupling inductors", IEEE Trans. Power Electron, vol. 16, no. 4, pp. 499, 507, Jul 2001.

- [12] Ilic. M, Maksimovic. D, "Interleaved zero-currenttransition buck converter", IEEE Trans. Ind. Appl., vol. 43, no. 6, pp. 1619,1627, Nov-Dec 2007.

- [13] Peng Xu, Jia Wei, Lee. F. C, "Multiphase coupled-buck converter-a novel high efficient 12 V voltage regulator module", IEEE Trans. Power Electron, vol. 18, no. 1, pp. 74, 82, Jan 2003.

- [14] X. Ruan, J. Wei, and Y. Xue, "Three-level converters with the input and output sharing the ground", in Proc IEEE PESC, pp 19191923, 2003.

- [15] Yao. K, Yang Qiu, Ming Xu, Lee. F. C, "A novel winding-coupled buck converter for high-frequency, high-step-down DC-DC conversion", IEEE Trans. Power Electron, vol. 20, no. 5, pp. 1017, 1024, Sept. 2005.

- [16] Xinbo Ruan, Bin Li, Qianhong Chen, Siew-Chong Tan, Tse. C, "Fundamental considerations of three-level DC-DC converters: topologies, analyses, and control", IEEE Trans. Circuits and Systems I: Regular Papers, vol. 55, no. 11, pp. 3733, 3743, Dec. 2008.

- [17] R. Miftakhutdinov, "Optimal Design of Interleaved Synchronous Buck Converter at High Slew-Rate Load Current Transients", Proceedings of Power Electronics Specialists Conference, vol. 3, Page(s): 1714 1718, June 2001.

- [18] M. Gerber, J. A. Ferreira, I. W. Hofsaer, and N. Seliger, "Interleaving optimization in synchronous rectified

DC/DC converters", in Proc. IEEE Power Electron. Spec. Conf., pp. 4655-4661, 2004.

- [19] R. Miftakhutdinov, J. Zbib, "Synchronous Buck Converter with Increased Efficiency", in Twenty Second Annual IEEE Applied Power Electronics Conference, pp. 714-748, Feb. 25-Mar. 1, 2007.

- [20] Weihong Qiu, S. Mercer, Zhixiang Liang, G. Miller, "Driver Dead time Control and its Impact on System Stability of Synchronous Buck Voltage Regulator", in IEEE Transactions on Power Electronics, vol. 23, no. 1, pp. 163-171, Jan. 2008.