Published Online March-April 2017 in IJEAST (http://www.iieast.com)

# ANALYSIS OF SWITCHED CAPACITOR MULTILEVEL INVERTER USING ALTERNATIVE PHASE OPPOSITION DISPOSITION PWM TECHNIQUE FOR VARIABLE FREQUENCY DRIVES

Beena M Varghese Professor, Department of EEE MA College of Engineering Kothamangalam, Kerala, India Bhagyalakshmi P S PG Scholar, Department of EEE MA College of Engineering Kothamangalam, Kerala, India Dr. Bos Mathew Jos Professor, Department of EEE MA College of Engineering Kothamangalam, Kerala, India

Abstract— Using parallel-series converter in as DC Power supply appliance gives a good opportunity to maintain stable supply while the load is changing. In this work, a new step up switched capacitor multilevel inverter is proposed. It consists of two parts such as a switched capacitor circuit and a full bridge inverter which are connected in parallel. Here a small input voltage can be used to produce a boosted output voltage. Number of switches used is very less compared to the conventional inverter. The multilevel dc output voltage of the circuit in the first part becomes the input of the circuit in the second part, resulting in a stepped voltage waveform. Such waveform is close to a sinusoidal and its harmonic content also very less compared to the conventional multilevel inverter by using the Alternative Phase Opposition Disposition (APOD) PWM control strategy. This inverter outputs larger voltage than the input voltage by switching the capacitors in series and in parallel. The maximum output voltage is determined by the number of the capacitors. Unlike the conventional inverters, this topology does not uses a complicated control scheme or isolated dc sources. Also output frequency can be varied by varying the modulating signal frequency. In this paper, the circuit configuration, the theoretical operation, the simulation results with MATLAB/SIMULINK.

Keywords— Multilevel Inverter, charge Pump, Charging, Single DC Source, Switched Capacitor

### I. INTRODUCTION

In recent years, a power electronic system plays a important role in many areas of developing fields. With the sudden changes in electric fields, the power electronic devices are expected to handle the higher rating of voltage and capacity [1]-[4]. As a solution to this issue, multilevel inverters have gained much attention in recent years due to its several advantages.

Multilevel inverters produce a stepped output phase voltage with a refined harmonic profile when compared to a two-level inverter [1]. The concept of multilevel inverters,

introduced about 30 years ago [1], entails performing power conversion in multiple voltage steps to obtain improved power quality, lower switching losses, better electromagnetic compatibility and higher voltage capability. Nowadays, there exist three commercial topologies of multilevel voltage source inverters: the most popular being the diode-clamped, flying capacitor and cascaded H-bridge [2] [4] structures. These inverters with multiple numbers of levels are more efficient than the two level inverter. But at the same time it has some drawbacks like more no of switching devices, cost etc. Some of the other topologies like the conventional H- bridges use multiple numbers of dc sources to obtain large number of levels in the output.

The diode clamped or neutral point clamped has the difficulty of increase in the number of clamping diodes as level increases. Similarly, in case of flying capacitor multilevel inverter the number of capacitors increases and system becomes bulkier. Among these inverter topologies, cascaded multilevel inverter reaches the higher output voltage and power levels, and the higher reliability due to its modular topology and the simplicity. In all the above topologies, the peak amplitude value of the output will be only the source voltage, with the rest of the levels being only a fraction of input voltage. An advantage of multilevel inverter is the harmonic reduction in the output waveform. As the number of levels increases, the output THD reduces. The multilevel inverter has lesser harmonics compared to the conventional two level inverter. In normal condition when amplitude modulation index is one that time magnitude of output voltage of inverter is same as input voltage. So that we have to use dc/dc boost converter to increase output voltage levels to ensure output voltage is to be greater or at output side we have to use inductors or transformer but at higher power transformer should withstand heavy magnetic core so that it can sustain higher power which increases size of whole inverter assembly.

There issues are considered since battery technologies haven't evolved too much. Almost in every application lead acid batteries have proven their potential at lower cost. By reducing size of inverter assembly we can increase the size of

Published Online March-April 2017 in IJEAST (http://www.ijeast.com)

these batteries which are in beneficial to end consumers of such products. As a provision against the issue, a charge pump, which does not have any inductors, is applied to such systems. A charge pump output a larger voltage than the input voltage with switched capacitors. When the several capacitors and the input voltage sources are connected in parallel, the capacitors are charged. When the several capacitors and the input voltage sources are connected in series, the capacitors are discharged. The charge pump output the sum of the voltages of the capacitors and the input voltage sources. However, a charge pump has many switching devices which make the system more complicated.

As a solution for all the disadvantages, a new switched capacitor multilevel inverter is implemented. A switched-capacitor (SC) inverter outputs multilevel voltages with switched capacitors. An SC inverter is similar to a charge pump in the topology. The new boost switched capacitor multilevel inverter produce greater output voltage than the input voltage. It makes use of only one dc source as the input and the number of switching devices is reduced when compared to the widely used conventional topologies. This multilevel inverter does not have any inductors which make the system small. The output harmonics of the novel multilevel inverter are reduced by the multilevel output. Another advantage is the input required to obtain a particular output voltage is very less compared to the existing inverters.

## II. CIRCUIT TOPOLOGY OF SEVEN LEVEL INVERTER

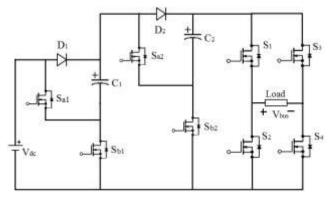

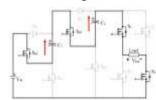

A Switched Capacitor network is a cirsuit used to generate a greater voltage waveform [8]. The staircase output voltage generated by this inverter is the output from the full bridge inverter and the input voltage source for the full bridge inverter is the output from the capcitor circuit. Thus output voltage obtained is greater than the input voltage. The switches in the SC network and full bridge inverter are operated in the high switching frequency. A new step up switched-capacitor (SC) multilevel inverter is formed by cascading two parts, a switched capacitor network and a full bridge inverter [6],[7], [8] shown in figure 1.

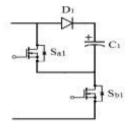

The basic switched capacitor cell is developed using one capacitor, two switching devices with one diode as shown in figure 2. Each of these cells are connected in parallel with each other to increases the number of levels that is desired in the multilevel output. Each of the cells is made to operate as a parallel-series converter. Each switched capacitor cell is reduced by one switch. When a switch is turned ON, input source and capacitor becomes in parallel and the diode conducts.

Fig. 1. Circuit diagram of Proposed Seven Level Inverter

. When its turned OFF and complementary switch is ON, the capacitor becomes in series with the input voltage source and the diode is OFF.

Fig. 2. Switched Capacitor Cell

A voltage source  $V_{\rm dc}$  is the input voltage source. By proper switching of the devices the capacitor are charged to the source voltage at first, then for obtaining the required level of output voltage the switches are turned ON and OFF in a way that only the required capacitor becomes in series with the sources and the load

For N number of cells, the new multilevel inverter generates (2N+3) levels in the output voltage waveform. Number of switches used is very less compared to the conventional inverter.

## III. OPERATING PRINCIPLE OF SEVEN LEVEL INVERTER

A switched capacitor seven level inverter is analysed using two SC cells in parallel (N=2). The inverter output voltage is larger than the input voltage by proper switching of SC cells. The capacitors are charged by connecting capacitor and the input voltage source in parallel. And capacitors are discharged when capacitor and the input voltage source are connecting in series. The switching control pulses for the different switches are developed by using the several multi carrier PWM techniques. The working of inverter can be illustrated by the main three steps;

- 1. All the capacitors are charged

- 2. Some of the capacitors are discharged

- 3. All the capacitors are discharged

The basic operations of the inverter are used to obtain a positive and negative cycle for the multilevel output. The positive half cycle is obtained with switches  $S_1$  and  $S_4$  of full bridge inverter ON and negative half cycle with switches  $S_2$  and  $S_3$  of inverter ON.

Published Online March-April 2017 in IJEAST (http://www.ijeast.com)

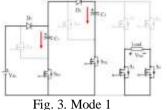

## A. Mode 1 ( $V_{bus} = 0 V$ )

Switches  $S_{b1}$ ,  $S_{b2}$  are ON and  $S_{a1}$ ,  $S_{a2}$  are OFF. Diodes  $D_1$ ,  $D_2$ conducts during this period. All capacitors are in parallel with input as shown in figure 3. Switches of the full bridge inverter of the same upper/lower limb conducts.

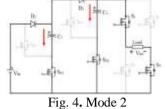

B. Mode 2 ( $V_{bus} = V_{dc} - 2V_f$ )

Switches  $S_{b1}$ ,  $S_{b2}$  are ON and  $S_{a1}$ ,  $S_{a2}$  are OFF. Diodes  $D_1$ ,  $D_2$ conducts during this period. All capacitors are in parallel with input. Switch S<sub>1</sub> and S<sub>4</sub> of the full bridge inverter conducts as shown in figure 4.

## C. Mode 3 $(V_{bus} = V_{dc} + V_{C1} - V_f)$

Switches  $S_{b1}$ ,  $S_{b2}$  and  $S_{a2}$  are turned OFF and  $S_{a1}$  is ON. Switches S<sub>1</sub> and S<sub>4</sub> of full bridge inverter are ON. As a result  $C_1$  is in series and  $C_2$  is in parallel as shown in figure 5.

Fig. 5. Mode 3

Fig. 6. Mode 4

## D. Mode 4 $(V_{bus} = V_{dc} + V_{C1} + V_{C2})$

In this mode all the capacitors are connected in series. The capacitor C1 and C2 are connected in series with the source voltage as shown in figure 6. This is obtained by switching OFF S<sub>b1</sub>, S<sub>b2</sub> and simultaneous turning ON of switches S<sub>a1</sub> and  $S_{a2}$ . The switches  $S_1$  and  $S_4$  of full bridge inverter are conducting in this period.

Similarly the negative half cycle can be obtained by turning on  $S_2$  and  $S_3$  instead of  $S_1$  and  $S_4$ , thus seven level output can be obtained.

## IV. SYSTEM ANALYSIS

## A. Number of Levels and Maximum output value

The maximum output voltage level is determined by the number of switched capacitor cell connected to the network. If 'N' is the number switched capacitor cells, then number of output level and maximum output value is given by the relation

No. of output levels,

$$m = 2N+3$$

(1)

Maximum output voltage =

$$(N+1)V_{dc}$$

(2)

## B. Voltage stress across the Switches

The maximum voltage dropped is the output voltage which is across the full bridge switches (S<sub>1</sub>, S<sub>2</sub>, S<sub>3</sub> & S<sub>4</sub>) and minimum voltage dropped is across the switches in the switched capacitor cell. If N is the number of SC cells;

Voltage stress across the full bridge switches  $(S_1, S_2, S_3 \& S_4)$

$$V_{fullbridge} = (N+1) V_{dc} \tag{3}$$

Voltage across the switches in SC network,

Voltage across switch

$$S_{al}$$

,  $V_{sal} = V_{dc}$  (4)

Voltage across switch

$$S_{b1}$$

,  $V_{sb1} = V_{dc}$  (5)

Voltage across Switch

$$S_{a2}$$

,  $V_{sa2} = V_{dc} - V_f$  (6)

Voltage across Switch

$$S_{b2}$$

,  $V_{sb2} = V_{dc} + V_{c1}$  (7)

Where, V<sub>dc</sub> is the input DC voltage

V<sub>f</sub> is the forward voltage drop of diodes N is the number of switched capacitor cells

## C. Voltage across the Diodes

Proposed inverter uses double number of diodes compared to the existing topology [3][4]-[9]. In which diodes in the upper limb of the SC cell undergoes high frequency switching and diodes in the lower limb of SC cell undergoes normal switching with different reverse biased voltages. All diodes are forward biased when common switch S<sub>b</sub> is turned ON.

Diode D<sub>1</sub> in the upper limb of SC cell is reverse biased by the capacitor voltage when switch Sal is turned ON and Diodes in the lower limb is reverse biased when the common switch S<sub>b</sub> is turns off.

Diode

$$D_1$$

in the upper limb,  $V_{DI} = -V_{cI}$  (8)

Diode D<sub>2</sub> in the lower limb,

$$V_{D2} = -V_{c2}$$

(9)

## D. Calculation of Capacitors

$$C = \frac{\Delta Q_i}{\Delta V_{Ci}} \tag{10}$$

Where,  $\Delta Q_i$  Change in charge over a period ΔV<sub>Ci</sub> Change in voltage over a period

The required capacitance and voltage ripple are inversely related to each other. An increase in the capacitance will decrease the amount of ripple [3].

$$\Delta V_{Ci} = (\% \, ripple) \, V_c \tag{11}$$

The capacitor C<sub>1</sub> and C<sub>2</sub> are discharged with switching S<sub>a1</sub> and  $S_{a2}$  respectively and capacitance  $C_i$  can be calculated as  $C_i = \frac{\Delta Q_i}{(\%ripple)V_c}$

$$C_i = \frac{\Delta Q_i}{(\%ripple)V_c} \tag{12}$$

## E. Switching Angle Calculation

For a multilevel inverter each level is occurred at a particular switching angle. Seven level inverter has three switching angles corresponding to three levels shown in figure 7. For any level inverter switching angles are calculated using the equation (12)

$$\theta_{j} = \sin^{-1}\left(\frac{2j-1}{m-1}\right)$$

$$\text{Where, } j = 1,2,\dots,\left(\frac{m-1}{2}\right)$$

$$m = \text{output levels}$$

(13)

Fig. 7. Calculation of Switching Angles

For the modified Switched Capacitor Inverter V<sub>1</sub>=3.4V, V<sub>2</sub>=8.4V and V<sub>3</sub>=12.6V and corresponding switching angles are  $\theta_1$ =0.1674rad,  $\theta_2$ =0.5236rad and  $\theta_3$ =0.9851rad.

## F. RMS Output Voltage

RMS value of the output voltage is calculated using the switching angles of each output step. For the seven level output three switching angles are generated. From results RMS value of output voltage can be calculated using the equation (13)

Published Online March-April 2017 in IJEAST (http://www.ijeast.com)

$$V_{rms} = \sqrt{\left(\frac{2}{\pi}\right)\left(V_1^2(\theta_2 - \theta_1) + V_2^2(\theta_3 - \theta_2) + V_3^2(\frac{\pi}{2} - \theta_3)\right)}$$

(14)

For the above given values,  $V_{rms} = 9.0855V$

RMS value of the fundamental output voltage component can be calculated using the step voltage and switching angle as shown in equation (14)

mown in equation (14)

$$V_{lrms} = \frac{V_1}{\sqrt{2}}$$

$$= \left(\frac{2\sqrt{2}}{\pi}\right) (V_1 \cos \theta_1 + (V_2 - V_1) \cos \theta_2 + (V_3 - V_2) \cos \theta_3)$$

$$= 9.0069V$$

(15)

## G. Total Harmonic Distortion

The main criterion for assessing the quality of the voltage delivered by an inverter is the Total Harmonic Distortion (THD). The THD is a ratio between the Root Mean Square (RMS) of the harmonics and the fundamental signal.

$$THD = \sqrt{\left(\frac{v_{rms}^2}{v_{1}^2 rms} - 1\right)}$$

(16)

For the Switched Capacitor Inverter, THD = 13.24%

## H. Voltage ripple of capacitor

For a switched capacitor cells, when the switch  $S_{\text{ai}}$  is turned OFF, capacitor  $C_i$  (i = 1, 2....N) starts charging to  $(V_{dc} - 2 V_f)$ and when switch Sai turned ON means the charging period of capacitor  $C_i$  ends shown in figure 3.

Voltage ripple of capacitor,

$$\Delta V_c = \frac{1}{c_i} \int_{t_0}^{t_1} i_0 dt$$

(17)

Where t<sub>0</sub> and t<sub>1</sub> are the start and end time of discharging period. For different PWM techniques t<sub>0</sub> and t<sub>1</sub> varies.

$$\Delta V_{Ci} = \frac{1}{2\pi f_s C_i} \int_{\theta_{1+i}}^{\pi^{-}\theta_{1+i}} i_0 \ d\omega t$$

$$= \frac{V_{in}}{2\pi f_s R C_i} [\pi - 2\theta_{1+i}]$$

$$= \frac{V_{in}}{2\pi f_s R C_i} \sum_{a=i}^{n} [\pi - 2\theta_{1+i}]$$

(19)

$$= \frac{V_{in}}{2\pi f_0 RC_i} [\pi - 2\theta_{1+i}] \tag{19}$$

$$= \frac{V_{in}}{2\pi f_s RC_i} \sum_{a=i}^{n} [\pi - 2\theta_{1+i}](a+1)$$

(20)

Voltage ripple of  $C_1$  and  $C_2$  are

$\Delta V_{c1} = 6.1298 * 10^{-4} \text{V}$  and  $\Delta V_{c2} = 2.7964 * 10^{-4} \text{V}$

## I. Conduction Losses

The conduction losses of switched capacitor cells occurred during charging process of the capacitor. When switch  $S_{ai}$  is turned OFF, the capacitor  $C_i$  (i = 1, 2....N) is charged to ( $V_{dc}$  – 2V<sub>f</sub>) through two forward biased diodes shown in figure 3, where V<sub>f</sub> is the forward voltage drop of a diode. For seven level inverter circuits two similar charging paths operated in parallel with a common switch of S<sub>b</sub>. The conduction losses during charging of Capacitor  $C_i$  are given by the equation (21)

$$P_{con} = \frac{f_s}{2} \sum_{i=1}^{p} C_i (V_f + \Delta V_{Ci}) \Delta V_{Ci}$$

(21)

Where, p is the number of capacitor charging parallel path

p, i = 1, 2.....N

f<sub>s</sub> is the switching frequency

N is the number of SC cell

Large capacitance reduces the voltage ripple, thereby reduces the power loss.

For 100mF capacitor and 1kHz switching frequency, conduction loss can be calculated as

$$P_{con} = 0.03573W$$

## J. Switching Losses

Switching losses occur during turning ON and turning OFF time and they dominate for the fast switching operations. When the switch is turned OFF, its voltage increases from 0 to maximum voltage. The switching loss  $P_{sw}$  of the switch during one switching cycle is given by the equation (22)

$$P_{sw} = f_s C_{ds} V_s^2 \tag{22}$$

$P_{sw} = f_s C_{ds} V_s^2$ Where,  $f_s$  is the switching frequency

C<sub>ds</sub> is the parasitic capacitance of MOSFET

$V_s$  is the voltage across the switch

For any full bridge inverter switch,  $V_s = 12.6V$ ,  $C_{ds} = 440PF$ and 1kHz switching frequency

$$P_{sw} = 6.98544*10^{-6} \text{ W}$$

### PULSE WIDTH MODULATION SCHEMES V.

To control and to generate high quality output waveform, an appropriate modulation scheme is required. Among the various modulation schemes, an important family of modulation technique, multicarrier pulse width modulation stands out because it offers significant simplicity and easy to implement switching waveforms.

For the Simulation Sinusoidal Alternative Phase Opposition Disposition (APOD) PWM technique is used, because APOD shows the minimum THD for all switching frequency [9]. The frequency ratio  $m_f$  is defined in the relation (23)

$$m_f = \frac{f_c}{f_c} \tag{23}$$

where, f<sub>c</sub> is the carrier (triangular) signal frequency f<sub>m</sub> is the modulating signal frequency

Carrier frequency or switching frequency is chosen as 1kHz for the optimum THD and modulating signal frequency as 50Hz. ie.,  $m_f = 20$ .

The amplitude modulation index  $m_a$  is defined as  $m_a = \frac{2A_m}{(m-1) A_c}$

$$m_a = \frac{2A_m}{(m-1)A_a} \tag{24}$$

where, A<sub>m</sub> is the amplitude of the modulating signal A<sub>c</sub> is the peak amplitude of the carrier signal

For an m-level inverter, (m-1) carriers with same carrier frequency  $f_c$  and same peak-to-peak amplitude  $A_c$  are continuously compared with the sinusoidal reference waveform having amplitude A<sub>m</sub> and reference frequency f<sub>m</sub>.

In Sinusoidal Alternative Phase Opposition Disposition (APOD) alternate carriers are phase shifted by 180° from its neighbour [6] - [9] as shown in figure 8.

Fig. 8. Sinusoidal Phase Disposition PWM

## VI. SIMULATION AND RESULTS

For an input of 5V, switching frequency f<sub>c</sub> as 1kHz and reference frequency f<sub>m</sub> as 50Hz, the proposed multilevel inverter was simulated in Matlab Ra2014a. The capacitance  $C_i$ can be determined properly with considering the voltage ripple of the capacitors  $C_i$ .

Published Online March-April 2017 in IJEAST (http://www.iieast.com)

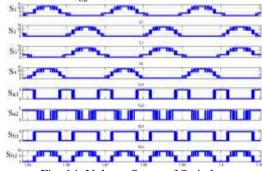

### A. Gate Pulse Generation

Fig. 9. Switching Pulses using APOD techniques

Gate signals are obtained by comparing modulating signal at fundamental frequency (50Hz) with triangular carrier signal which are at 1kHz frequency. Figure 9 shows the seven switching pulses using APOD technique.

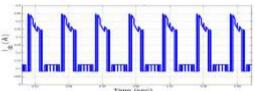

## B. Input current

Figure 10 shows the input current drawn by the circuit. Input current which is a combination of diode currents and switch current during the capacitor discharging period. Diode current is used to charge the capacitors when the switch  $S_{ai}$  is turned OFF. Maximum input current drawn from the input source is 0.45A.

Fig. 10. Input Current

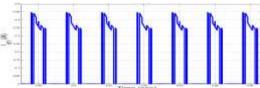

### C. Diode current

Figure 11 shows the current through the diodes. The maximum current is 0.45A during the charging period of capacitor, because capacitor is charged through input source, diodes  $D_{\rm i}$  and common switch  $S_{\rm bi}$ . Current through diode  $D_{\rm l}$  can be calculated by deducting the switch Sa1 current from the input current.

Fig. 11. Current through Diode D<sub>1</sub>

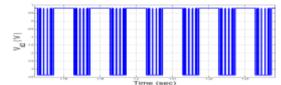

## D. Diode Voltage

Figure 12 shows the voltage across the diode D<sub>1</sub>. Diode D<sub>1</sub> experiences 0.8V forward drop and -4.2V reverse voltage.

Fig. 12. Voltage across Diode D<sub>1</sub>

Figure 13 shows the voltage across the diode  $D_2$ . From the waveform forward diode drop is 0.8V and -3.4V reverse voltage.

Fig. 13. Voltage across Diode D<sub>2</sub>

## E. Capacitor Voltage

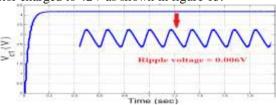

During  $S_{ai}$  turned OFF, capacitor  $C_I$  starts charging to a voltage equal to  $(V_{dc} - V_f)$  through forward biased diode  $D_I$ . In this work,  $V_{dc}$ = 5V and Forward diode drop,  $V_f$  = 0.8V means capacitor charged to 42V as shown in figure 15.

Fig. 15. Voltage across Capacitor C<sub>1</sub>

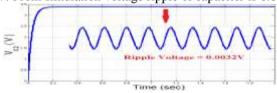

Capacitance ripple voltage from the simulation for  $C_1$  is 0.006V. The capacitor to be used should be such that it should retain the voltage specified. Figure 16 shows the voltage of capacitor  $C_2$ . Here capacitor  $C_2$  charges through two forward biased diodes. So  $C_2$  charged to a voltage equals to  $(V_{dc} - 2V_f) = 3.4V$ . From simulation voltage ripple of capacitor is 0.0032V.

Fig. 16. Voltage across Capacitor C2

## F. Voltage Stress Across the Switches

Figure 14 shows the voltage stress using APOD PWM technique. From the simulation, voltage drop across the switches in the full bridge inverter is 12.6V. Voltage stress across switch  $S_{a1}$  and  $S_{b1}$  is 5V, for  $S_{a2}$  is 4.2V and maximum stress across switch  $S_{b2}$  is 9.2V.

Fig. 14. Voltage Stress of Switches

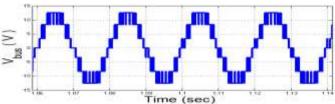

## G. Output Voltage and output current (R LOAD)

. Figure 17 show the seven level output voltage using Alternative Phase Opposition Disposition PWM technique.

Published Online March-April 2017 in IJEAST (http://www.ijeast.com)

Fig. 17. Output Voltage (R Load)

Figure 18 shows the Seven level output current of the inverter using  $100\Omega$  load resistance.

Fig. 18. Output Current (R Load)

## H. FFT Spectrum

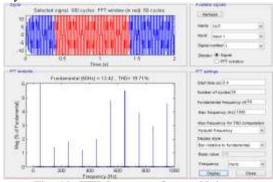

Figure 19 shows the FFT spectrum of output voltage using the Alternative Phase Opposition Disposition technique with a modulation index  $m_a=1$ . Here %THD is calculated by considering 30 cycles of output voltage with a fundamental frequency of 50Hz.

Fig. 19. FFT Spectrum Output Voltage

## I. Filter Circuit

A typical capacitor input filter consists of a filter or reservoir capacitor  $C_1$ , connected across the rectifier output, an inductor L, in series and another filter or smoothing capacitor,  $C_2$ , connected across the load, R. Assuming  $C_1 = C_2 = C$ ,

Capacitor,  $C = \frac{1}{4\pi^2 L f_c^2}$  (31) Cut-off frequency,  $f_c = \frac{1}{2\pi\sqrt{LC}}$  (32)

Fig. 20. Filter Output Voltage

Figure 20 shows the output voltage of the inverter using filter.

## VII. VARIABLE FREQUENCY DRIVES

## A. Power Grid Applications

Basically, a typical GCPV system consists of PV array, maximum power point tracker (MPPT) unit(s) or DC-DC converter, inverter and utility grid. The produced DC power is then converted into AC power using inverter before delivered into the utility grid. This inverter is acts as boosted DC-AC converter. So the input DC required to generate the grid voltage is less compared to other multilevel configuration and number of series connected module in the PV array can also be reduced. The three phase structure for a switched capacitor multilevel inverter can be implemented by combining three individual inverter blocks for each phase connected together. As the number of level in the output increases input DC required is reduces. Thus the size of entire system minimized because boost converter design can be eliminated. Eleven level three phase inverter output voltage is shown in figure 21.

Fig. 21. Three Phase Output Voltage

## **B.** Variable Frequency Drives

Modified Three Phase Series/Parallel Switched Capacitor Topology is applied to the Induction machine Drive. Here by varying the modulating signal frequency, this inverter can be used for Variable Frequency Drives [20].

## **Machine Parameters**

Ratings of Three Phase Induction Motor:

Voltage (line-line) = 460 V

Frequency f = 50 Hz

Nominal power of motor  $P_o = 7.5 \text{ kW}$

Rated speed  $N_r = 1440 \ rpm$

Rated current  $I = 2.650 \, A$

Load torque  $T_l = 47.5 N-m$

No. of poles P = 4

Parameters of Three Phase Induction Motor:

Stator Resistance  $R_s = 0.6 \Omega$

Stator leakage Inductance  $L_{ls}$ = 4.5 mH

Rotor Resistance  $R_r = 0.7 \Omega$

Rotor leakage Inductance  $L_{lr} = 4.5 \ mH$

Mutual Inductance  $L_m = 80 \text{ mH}$

Moment of Inertia J = 0.1 kg-m2

## 1. Modulating Signal Frequency $f_m = 50Hz$

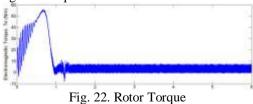

Fig. 22 shows the Electromagnetic Torque applied to induction machine Drive. Simulation is carried out for a zero reference electromagnetic torque.

Published Online March-April 2017 in IJEAST (http://www.ijeast.com)

Fig. 23 shows the Rotor speed of the induction machine Drive. From the simulation result we can say that the induction motor drive nearly catches the rotor speed and we can get the desired speed variation. Although there are changes in speed, the actual torque of the motor is almost near to the reference torque. There are some distortions in actual torque at the point where speed is drastically changing.

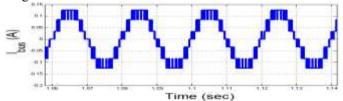

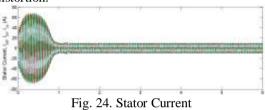

Fig. 24 shows the Stator Current in each phase of the induction machine Drive, which are almost near to sinusoidal and having lesser distortion.

## 2. Modulating Signal Frequency $f_m = 60$ Hz

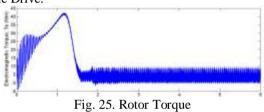

Fig.25 shows the Electromagnetic Torque applied to induction machine Drive.

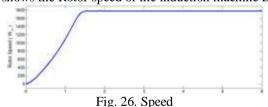

Fig.26 shows the Rotor speed of the induction machine Drive.

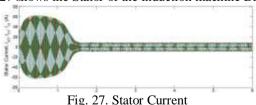

Fig.27 shows the Stator of the induction machine Drive.

guency of the modulating signal

As the frequency of the modulating signal varies motor performance varies, time at which reference torque occurs varies.

## VIII. CONCLUSIONS

In this paper, a switched capacitor boost multilevel inverter with reduced number of switches was developed and it was simulated in MATLAB/Simulink software. Alternative Phase Opposition Disposition PWM with a reference signal of 50 Hz and carrier of 1.6 kHz were used to generate gate pulses. Gate pulses generated are verified according to the switching pattern in simulation result. A multilevel output is simulated with a higher voltage by using only a small input voltage and it was determined that as the number of levels increases in the output, the input required to generate a particular output decreases considerably. At each level the voltage increases that is it doubles triples etc per level. Also it was seen by FFT analysis that % THD value decreases with increase in level. The total harmonic distortion was seen to be reduced to 19.78% for seven level output with 12.6 V as amplitude for an input of 5V. By varying the modulating signal frequency, this inverter can be used for Power Grid Applications and Variable Frequency Drives.

## IX. REFERENCES

- [1]. Akira Nabae, Isao Takashi, "A New Neutral-Point-Clamped PWM Inverter", *IEEE transaction on industrial applications*, Vol. IA-17, No. 5. September/October 1981.

- [2]. Jos Rodrguez, Jih-Sheng Lai and Fang Zheng Peng, "Multilevel Inverters: A Survey of Topologies, Controls, and Applications", 2008 IEEE transaction on industrial electronics, Vol. 49, No. 4, August 2002.

- [3]. S.S. Deshmukh, H.T.Jadhav, "Effective Loss Reduction Analysis in New Switched- Capacitor Boost-Multilevel Inverter Using Series/Parallel Conversion", 2014 IEEE Students Conference on Electrical, Electronics and Computer Science, 978-1-4799-2526-1/14, 2014.

- [4]. Elyas Zamiri, Naser Vosoughi, "A New Cascaded Switched-Capacitor Multilevel Inverter Based on Improved Series-Parallel Conversion with Less Number of Components", IEEE Transactions on Industrial Electronics, 2015.

- [5]. Bagher Karami, Reza Barzegarkhoo, Adib Abrishamifar and Mehdi Samizadeh, "A Switched Capacitor Multilevel Inverter for High AC Power Systems with Reduced Ripple Loss Using SPWM Technique", The 6th International Power Electronics Drive Systems and Technologies Conference (PEDSTC2015), 3-4 February 2015 IEEE.

- [6]. Janusz A. Starzyk, Ying-Wei Jan, and Fengjing Qiu "A DC–DC Charge Pump Design Based on Voltage Doublers", *IEEE Transactions on Circuits And Systems—I: Fundamental Theory And Applications*, VOL. 48, NO. 3, MARCH 2001.

- [7]. M.Kanimozhi, P Geetha, "A New Boost Switched Capacitor Multilevel Inverter Using Different Multi Carrier PWM Techniques", 2014 International Conference on Circuit, Power and Computing Technologies [ICCPCT], 978-1-4799-2397-7/14, IEEE 2014.

- [8]. Amrita Mariam Varghese, Beena M Varghese, Elizabeth Sebastian, "FPGA based Single Phase Switched Capacitor

(UEAST)

Published Online March-April 2017 in IJEAST (http://www.ijeast.com)

- Boost Multilevel Inverter", APEC 2001. IJSRD-International Journal for Scienti\_c Research and Development , Vol. 3, Issue 07, 2015 | ISSN (online): 2321-0613.

- [9]. Bhagyalakshmi P S, Beena M Varghese, Dr. Bos Mathew Jos, "Switched Capacitor Multilevel Inverter With Different Modulation Techniques", 2017 International Conference on Innovations in information Embedded and Communication Systems (ICIIECS).

- [10]. Yuanmao Ye, K.W.E. Cheng, Junfeng Liu, and Kai Ding, "A Step-Up Switched- Capacitor Multilevel Inverter with Self Voltage Balancing", APEC 2001. IEEE Transactions On Industrial Electronics, 10.1109/TIE.2014.2314052, 2013.

- [11]. Y. Hinago and H. Koizumi, "A switched-capacitor inverter using series/ parallel conversion", Proc. *IEEE Int. Symp. Circuits*, *Syst* 2010, pp. 31883191.

- [12]. Pradyumn Chaturvedi , Rajesh Nema , "Switching losses and harmonic investigations in multilevel inverters", http://www.jr.ietejournals.org on Sunday, December 07, 2008, www. researchgate. net/publication /26570208.

- [13]. M D. Safia, T V V Pavan Kumar, "Design and Simulation of Grid Connected PVsystem Using Multilevel Inverters", *International Journal of Electrical and Electronics Engineering* (IJEEE), ISSN (PRINT): 2231 – 5184, Volume-4, Issue-2, 2013.

- [14]. Lalit Dutta, Raj Kiran B, V Siva Brahmaiah Rama, "Cascaded Multilevel Inverters for Photovoltaic Power System Applications", *International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering*, Vol. .4, Issue 7, July 2015.

- [15]. Adil Sarwar, Mohammad S. J. Asghar, "Simulation and Analysis of a Multilevel Converter Topology for Solar PV Based Grid Connected Inverter", Smart Grid and Renewable Energy, Scientific Research, 2011, 2, 56-62 doi:10.4236/sgre.2011.21007 Published Online February 2011.

- [16]. Dhivya Balakrishnan, Dhamodharan Shanmugam, K.Indiradevi, "Modified Multilevel Inverter Topology for Grid Connected PV Systems", American Journal of Engineering Research (AJER), Volume-02, Issue-10.

- [17]. Muhammad H Rashid, "Power Electronics Handbook: Devices, Circuits, and Applications", Second Edition, Academic Press.

- [18]. Dr. P S Bimbhra, "Power Electronics", Khanna Publishers, Delhi, 2012

- [19]. Ned Mohan, Tore M. Undeland, William P. Robbins, 'Power Electronics', John Wiley & Sons Publications, 3rd edition, 2006